计算机组成原理笔记(五)

六、中央处理器

1.$ CPU $的组成与功能

(1)基本组成

- 运算器:数据加工

- 控制器:程序执行/指令执行

- 取指令:$ Mem[PC++]\rightarrow IR $

- 执行指令:指令字$ \rightarrow $控制信号序列$ \rightarrow $数据通路

(2)主要寄存器

程序计数器:$ PC (Program\enspace Counter) $,如$ X86:EIP\enspace MIPS:PC $

指令寄存器:$ IR (Instruction Register) $,可选

地址寄存器:$ AR(Address\enspace Register) $,如$ MAR $,可选

数据缓冲寄存器:$ DR(Data\enspace Register) $,如$ MDR $,可选

累加寄存器:$ AC(Accumulate\enspace Count) $,可选

程序状态字:$ PSW (Program\enspace Status\enspace Word) $,如$ X86:\enspace EFLAGS $,而$ MIPS $无

(3)主要功能

- 取指令并执行指令的部件——$ CPU $

- 运算器功能

- 数据加工: 算术/逻辑运算

- 控制器功能

- 程序控制: 程序中指令执行顺序控制

- 操作控制: 将机器指令翻译成执行部件所需操作控制信号

- 时序控制: 控制操作信号的产生时间、持续时间

- 异常控制: 异常处理,外设交互

- 运算器功能

(4)操作控制器

取指令,将机器指令译码并生成执行部件控制信号序列;

建立正确的数据通路,从而完成指令的正确执行;

实现方法

硬布线控制器 (时序逻辑型) (硬件实现)

微程序控制器 (存储程序型) (软件实现)

2.数据通路

(1)概述

数据通路——执行部件间传送信息的路径

- 通路的建立由控制信号控制,受时钟驱动;

- 不同指令、同一指令在执行的不同阶段的数据通路不同;

- 分为共享通路(总线结构)和专用通路

数据通路抽象模型

数据通路与时钟周期

在不同的数据通路抽象模型中组合逻辑产生的延迟不同

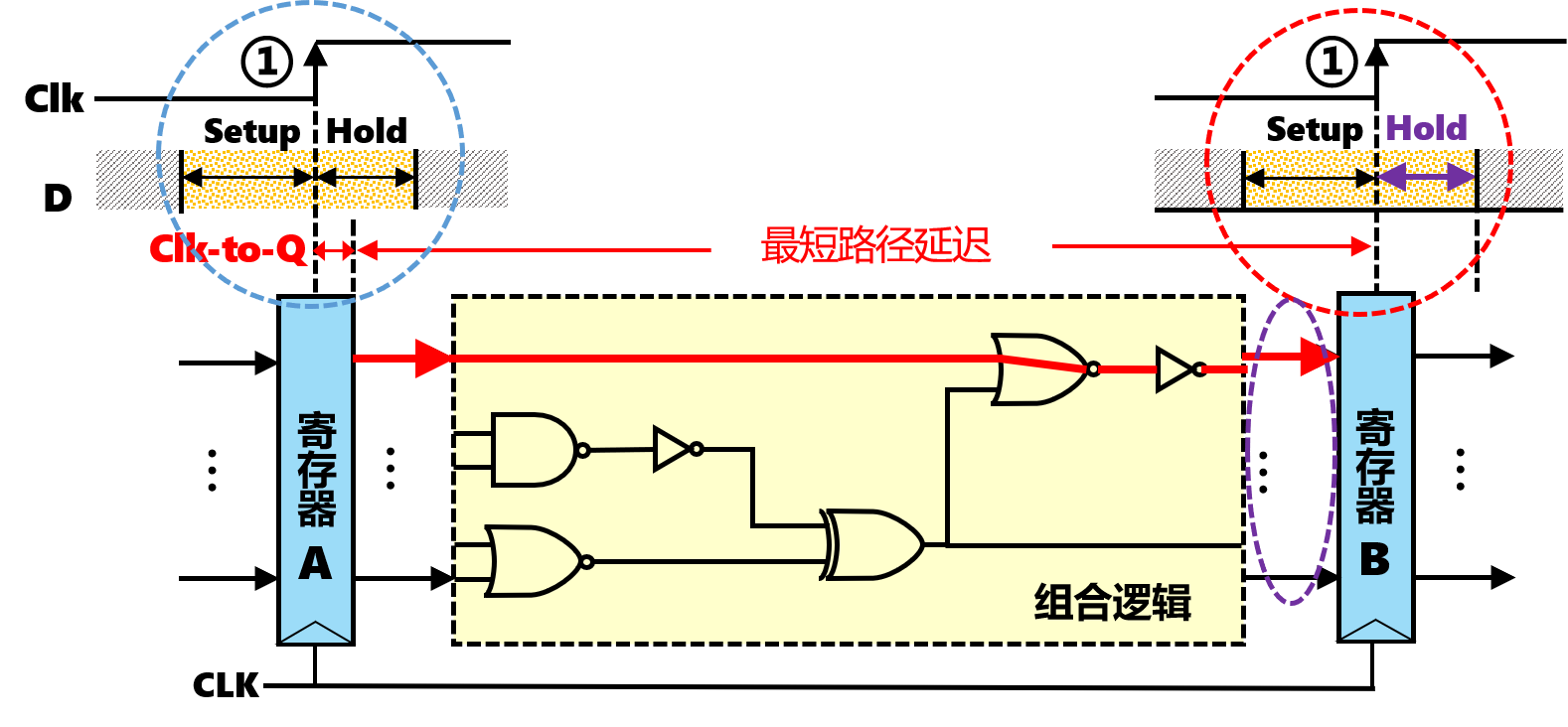

在$ D $触发器定时模型中,设如下定义:

- 时钟触发前,输入必须稳定一段时间,称为建立时间$ (Setup\enspace Time) $;

- 时钟触发后输入必须稳定一段时间,称为保持时间$ (Hold\enspace Time) $;

- 时钟触发到输出稳定的时间称为触发器延迟$ Clk\_to\_Q $

假设在如下寄存器传输模型中,将最长的传输路径称为最长关键传输路径,相应的有最短关键传输路径。

数据通路最小时钟周期>Clk_to_Q+最长关键路径时延+$ Setup\enspace Time $

Clk_to_Q+最短关键传输路径时延>$ Hold\enspace Time $

(2)不同总线结构的数据通路

共享通路(总线型)

- 主要部件都连接在公共总线上,各部件间通过总线进行数据传输

- 结构简单,实现容易,但并发性较差,需分时使用总线,效率低

专用通路

- 并发度高,性能佳,设计复杂,成本高

- 可以看作多总线结构

不同总线结构的数据通路对比

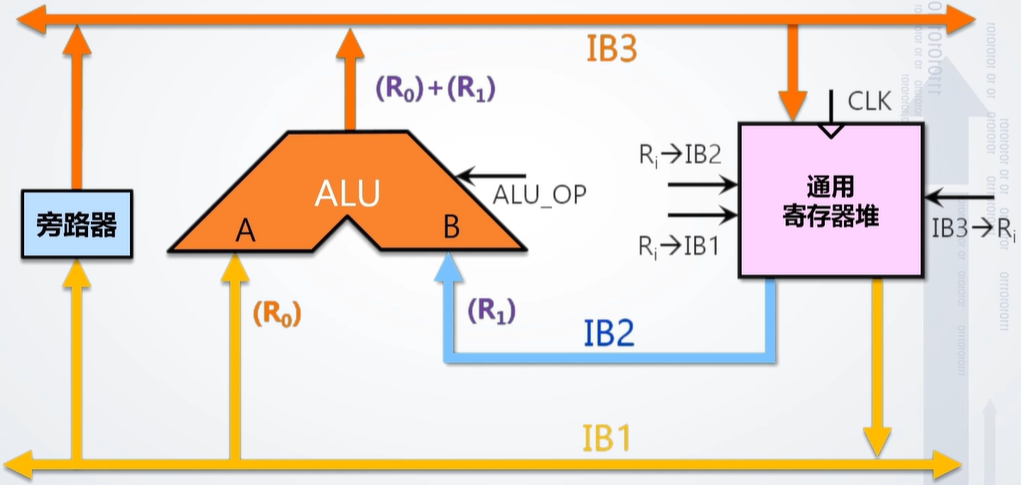

尝试使用以下不同总线结构执行$ ADD\enspace R_0,R_1 $指令

单总线结构:两个锁存器,$ 3 $个时钟周期

双总线结构:一个锁存器,$ 2 $个时钟周期

三总线结构:无需锁存器,$ 1 $个时钟周期

(3)单总线结构$ CPU $与数据通路

单总线$ CPU $实例

- 主要部件都连接在总线上

- 各部件间通过总线进行传输

- 控制信号说明

| 控制信号 | 作用信号 |

|---|---|

| $ IR_{out},PC_{out},\cdots,R1_{out} $ | 控制三态门将寄存器值输出到总线(互斥) |

| $ IR_{in},PC_{in},\cdots,R1_{in} $ | 控制寄存器使能端将总线数据锁存(时钟驱动) |

| $ +1\enspace ADD\enspace SUB $ | 运算控制信号(互斥) |

| $ Write\enspace Read $ | 内存读写控制信号(时钟驱动) |

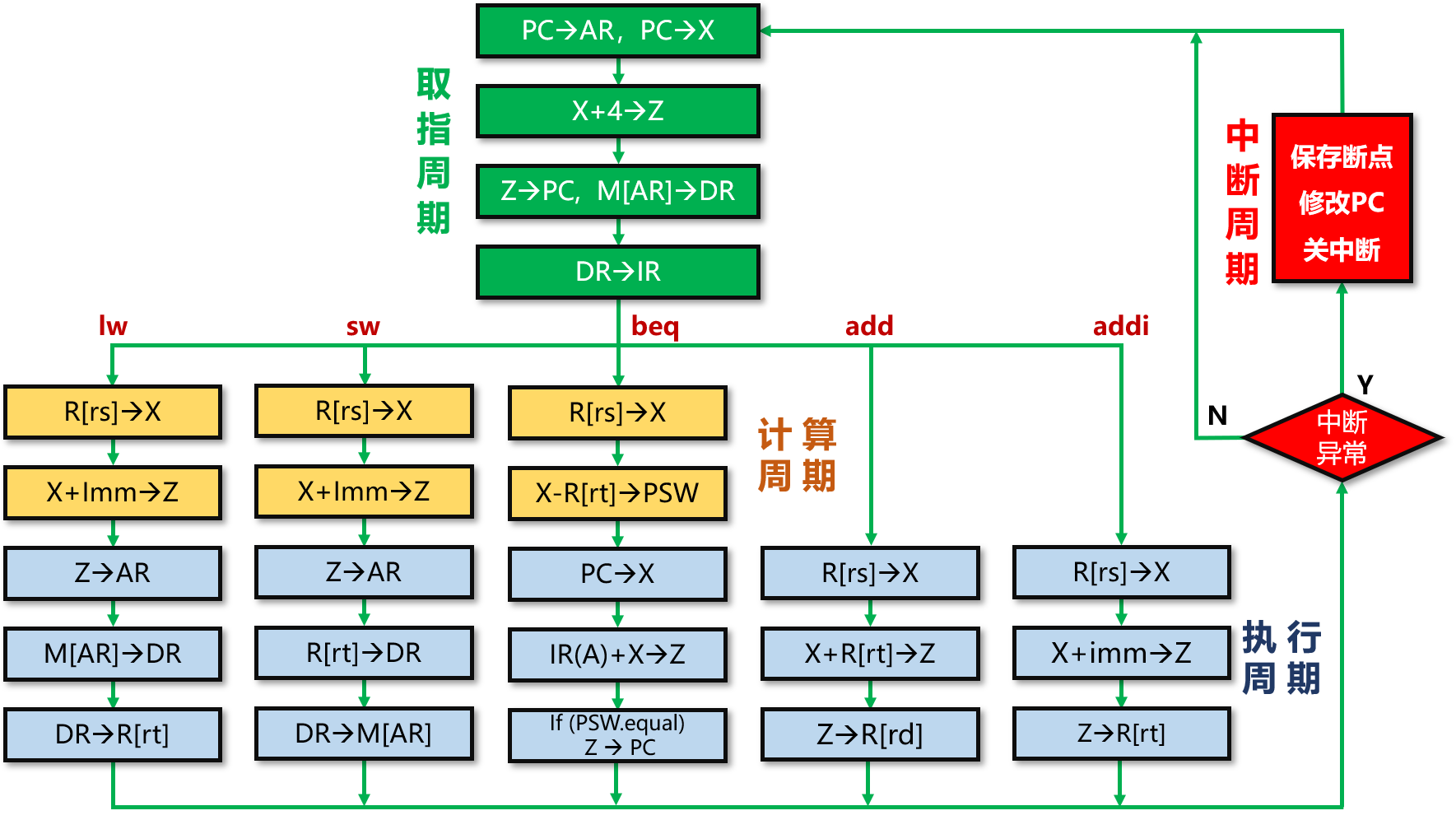

单总线$ MIPS\enspace CPU $模型下不同指令的数据通路

使用的$ MIPS\enspace CPU $模型

使用的$ MIPS $指令功能

| # | 指令 | 指令功能 |

|---|---|---|

| $ 1 $ | $ lw\enspace rt,imm(rs) $ | $ Mem[R[rs]+imm]\rightarrow R[rt] $ |

| $ 2 $ | $ sw\enspace rt,imm(rs) $ | $ R[rt]\rightarrow Mem[R[rs]+imm] $ |

| $ 3 $ | $ beq\enspace rs,rt,imm $ | $ if(R[rs]==R[rt])\quad PC+4+IMM\lt \lt 2\rightarrow PC $ |

| $ 4 $ | $ add\enspace rd,rs,rt $ | $ R[rs]+R[rt]\rightarrow R[rd] $ |

| $ 5 $ | $ addi\enspace rt,rs,imm $ | $ R[rs]+imm\rightarrow R[rt] $ |

指令周期方框图(数据流)

3.指令周期

指令执行的流程

- 如图所示,取指令、执行指令反复循环,其中白色圆圈的步骤可选

- 指令功能、寻址方式不同,数据通路、 执行时间不同,如何安排时序?

指令周期、机器周期和时钟周期

- 时钟周期$ = $节拍脉冲$ = $震荡周期——能完成一次微操作

- 机器周期$ =CPU $周期:从主存读出一条指令的最短时间——可完成复杂操作

- 指令周期:从主存取一条指令并执行指令的时间

- 指令周期包含$ 0\sim n $个机器周期,机器周期包含$ k $个节拍

指令控制同步

不同指令的功能不同,所需的机器周期数不同,因此有不同的时间控制方式

- 定长指令周期

- 一条指令执行所需的机器周期数固定,每个机器周期的时钟周期数固定

- 按机器周期同步,如$ MIPS $单周期,只需一个机器周期即可完成指令

- 变长指令周期

- 一条指令执行所需的机器周期数可变,每个机器周期的时钟周期数可变

- 按时钟周期同步,如$ MIPS $多周期

- 定长指令周期

4.时序与控制

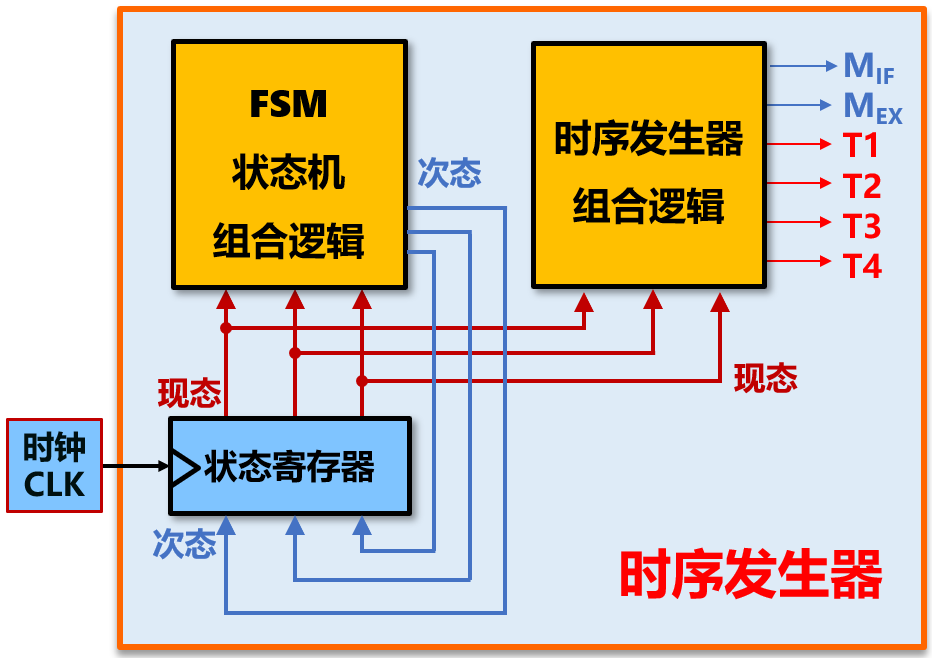

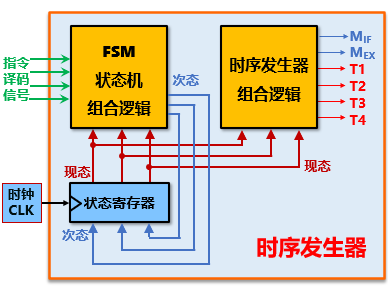

(1)时序发生器

- 循环产生周期电位、节拍电位,供控制器对信号进行时间调制

(2)早期三级时序系统与现代时序系统

- 早期三级时序系统包括状态周期、节拍电位、节拍脉冲三级时序

- 现代时序系统不再区分各级时序,定时信号就是基本时钟信号

(3)定长指令周期三级时序(同步控制)

特点

- 机器周期数、节拍数固定,设计简单,效率较低

- 时序发生器中不需要输入指令译码和反馈信号

- 下跳沿改变状态机,上跳沿改变寄存器锁存

指令周期、机器周期与时钟周期的关系

- 使用状态周期电位(电平信号)表示当前处于什么机器周期

- 使用节拍电位表示处于机器周期的哪个节拍

- 使得时钟脉冲$ \rightarrow $机器周期电位和节拍脉冲信号

- 使得硬布线控制器$ \rightarrow $组合逻辑电路

- 如:$ MemRead=M_{IF}\cdot(T_2+T_3)+Load\cdot M_{EX}\cdot(T_2+T_3) $

- 精准控制信号的产生时间与持续时间

设计时序发生器

首先实现状态机

- 根据现态和次态作出真值表得到$ FSM $状态机组合逻辑

采用计数器逻辑,循环计数

根据现态和各周期电位、节拍电位信号输出得到时序发生器组合逻辑

(4)变长指令周期三级时序(同步控制)

特点

- 机器周期数可变、节拍数可变,无周期浪费,更加灵活

- 根据指令类型决定完成取指令周期后跳转到哪个指令的对应周期

指令周期、机器周期与时钟周期的关系

设计时序发生器

首先实现状态机

时序发生器

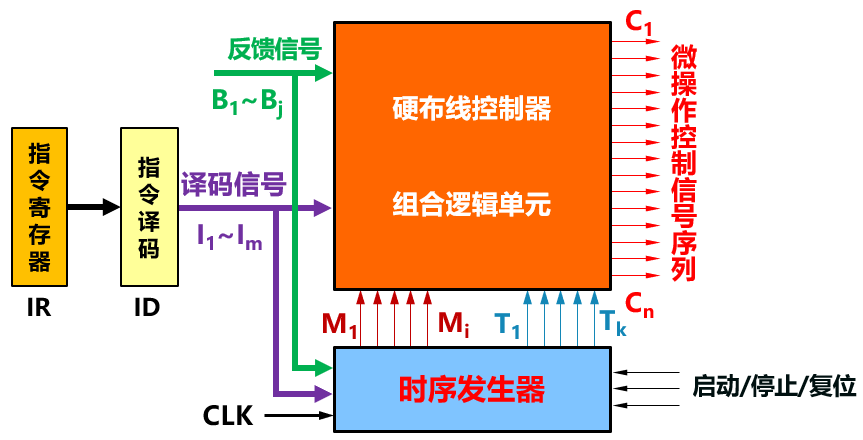

5.硬布线控制器

(1)基本原理

- 基本原理图

- 控制器:产生控制信号序列的逻辑电路——将机器指令字翻译为控制器信号序列

- 输入信号:指令译码,时钟,反馈信号

- 输出信号:功能部件控制信号序列

(2)三级时序硬布线控制器

引入时序产生器的三级时序硬布线控制器

将时序发生器从操作控制器中分离(分为定长指令周期和变长指令周期

将时序发生器输出的信号输入至硬布线控制器单元,产生控制信号序列

控制信号序列可以由译码信号、周期电位信号、节拍电平信号、反馈信号进行逻辑组合得到,其表达式为$ C_n=\sum\limits_{m,i,k,j}(I_m\cdot M_i\cdot T_k\cdot B_j) $

设计步骤

- 分析数据通路,画指令周期流程图,明确各节拍控制信号

- 设计时序发生器:根据机器周期、节拍划分构建状态图

- 找出同一微操作控制信号产生条件

- 写出各微操作控制信号的逻辑表达式

- 利用组合逻辑电路实现

(3)现代时序硬布线控制器

现代时序硬布线控制器

特点

现代时序系统不需要设计时序发生器,将每个节拍都作为一个状态

状态转换图

- $ C_n=f(x) $,x表示次态

直接将状态寄存器的现态作为硬布线控制器组合逻辑电路的输入

逻辑实现

设计步骤

- 分析数据通路,画指令周期流程图,明确各节拍控制信号

- 绘制指令执行状态转换图

- 构建状态转换表

- 实现有限状态机组合逻辑

- 实现控制器组合逻辑电路

(4)硬布线控制器的特点

- 结构复杂,无规则

- 设计和调试困难

- 不可改变指令系统和指令功能

- 速度快

6.微程序控制器

(1)工作原理

- 微程序是利用软件思想设计硬件的技术

- 控制信号序列可以像程序一样存储起来

- 控制信号序列分解为若干节拍

- 一个节拍的并发信号编成一条微指令

- 多个节拍对应多条微指令,形成一段微程序

- 依序执行微程序即可生成控制信号序列

- 指令取指执行$ \rightarrow $微程序执行$ \rightarrow $微指令执行$ \rightarrow $生成控制信号

- 软时序:依次执行微指令,时间信号有先后顺序

- 控制信号序列可以像程序一样存储起来

- 存储技术和程序设计相结合,回避复杂时序逻辑设计

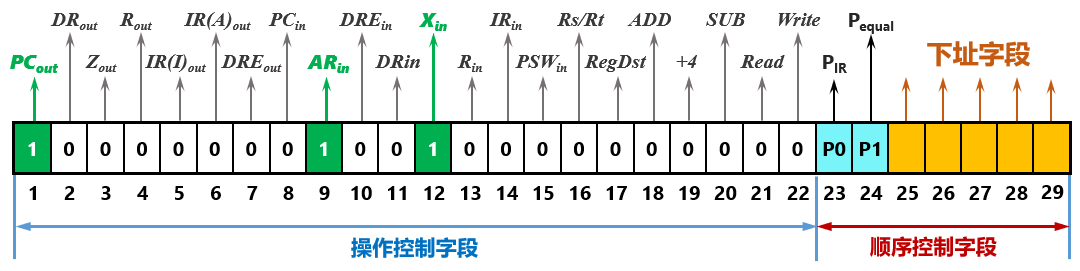

(2)微指令格式

操作控制字段:存储操作控制信号

- 每一位对应一个控制信号,也称微命令

- 可同时给出多个操作信号

顺序控制字段:用于控制微程序的执行顺序

- 判别字段为零,下一条微指令地址从下址字段获取

- 判别字段不为零,按约定规则生成下一条微指令地址

格式特点

- 一条微指令对应一个时钟周期

- 微指令操作控制字段的信号在当前时钟周期内有效,为$ 1 $有效

- 指令需要多少时钟周期就包括多少微指令

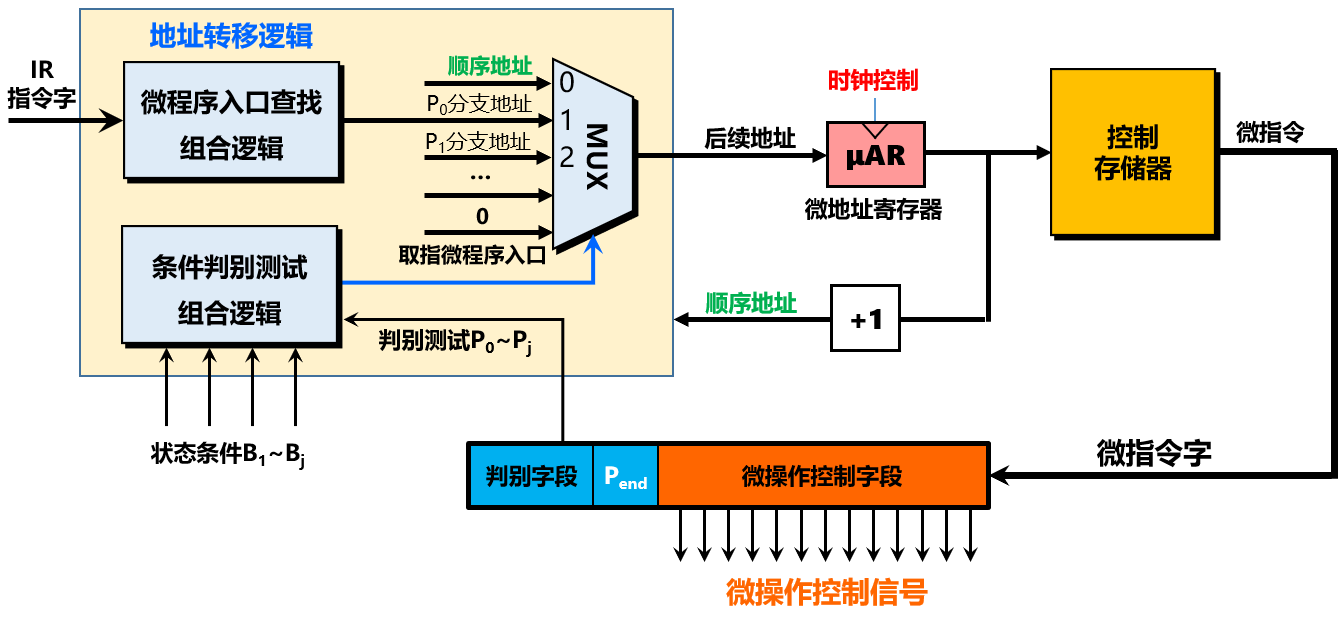

(3)微指令执行原理

- 初始化:$ μAR=0 $ , $ 0 $号地址为取指微程序入口

- 顺序执行取指微程序,最后一条微指令判别字段非零,地址跳转

地址转移逻辑原理

- 每个判别测试位对应一个微程序分支地址

主存与控制存储器

| 存放内容 | 存储容量 | 存储字长 | 存储速度 | 介质 | |

|---|---|---|---|---|---|

| 主存 | 数据与程序 | 大 | 机器字长 | 慢 | $ RAM $ |

| 控制存储器 | 微程序 | 小 | 微指令长度 | 快 | $ ROM/RAM $ |

(4)微程序设计

设计原则

- 有利于缩短微指令字长度

- 有利于减少控制存储器容量

- 有利于提高微程序执行速度

- 有利于对微指令进行修改

- 有利于提高微程序设计的灵活性

微指令编码

直接表示法

- 简单直观,便于输出控制,但是微指令长度太长,控存容量大

- 直接表示$ \rightarrow $编码表示——压缩互斥性微命令(最短为$ 18 $位)

- 下址字段$ \rightarrow $计数器法——$ μAR++ $,需要增加$ P_{end} $判别位

- 水平型$ \rightarrow $垂直型微指令——牺牲并行性

编码表示法

压缩互斥性微命令

- 思考:如果互斥的输出控制信号$ 8 $个,编码后长度多少?

计数器法

(5)硬布线与微程序对比

- 硬布线:同步逻辑、繁,快,贵,难改

- 一条指令多个时钟周期、一个时钟周期一个状态、一个状态对应一组并发信号

- 适合$ CISC $等功能较复杂的系列机$ X86 $、$ IBM\enspace S/360 $

- 可写控存方便修复出厂故障——$ Intel\enspace Core\enspace 2 $、$ Intel\enspace Xeon $

- 微程序:存储逻辑、简、慢、廉,易改

- 控制流存储为微指令微程序,一个状态对应一条微指令

- 一条指令对应多条微指令、状态字等同与存储器地址

- 适合$ RISC $计算机,如$ MIPS $、$ ARM $

7.异常与中断处理

中断的处理过程

关中断

临时禁止中断请求,是为了保障中断响应周期以及中断服务程序中保护现场操作的完整性;

保存断点

保存将来返回被中断程序的位置,对于已经执行完毕的指令其断点是下一条指令的位置(注意有可能不是顺序指令),对于缺页故障,段错等执行指令引起的故障异常,由于指令并没有执行,所以断点应该是异常指令的 PC 值。

中断识别

根据当前的中断请求识别出中断来源,也即发生了什么中断,并将对应中断的中断服务程序入口地址送程序计数器$ PC $

中断异常处理的数据通路

- 为了支持中断添加的相关支持

- 开关中断:增加$ IE $寄存器

- 保存断点:增加$ EPC $寄存器/堆栈

- 中断识别:增加中断控制逻辑

- 软件支持:$ eret $指令支持

- 添加的相关信号

- $ EPC_{in} $,$ EPC_{out} $

- 开中断$ STI $,关中断$ CLI $

- $ IntA_{out} $:将中断服务程序地址送入地址总线

- $ ClrInt $:清空正在响应的中断请求

- 中断响应周期的操作与控制信号

- 节拍$ T_1 $:$ 0\rightarrow IE $,$ PC\rightarrow EPC $,关中断并保存断点

- 控制信号:$ CLI $,$ PC_{out} $,$ EPC_{in} $

- 节拍$ T_2 $:中断程序入口$ \rightarrow PC $,中断服务程序地址送入$ PC $

- 控制信号:$ IntA_{out} $,$ PC_{in} $

- 节拍$ T_1 $:$ 0\rightarrow IE $,$ PC\rightarrow EPC $,关中断并保存断点

- $ eret $指令执行周期的操作与控制信号

- 节拍$ T_3 $:$ EPC\rightarrow PC $,$ 1\rightarrow IE $,恢复断点并开中断

- 控制信号$ EPC_{out} $,$ PC_{in} $,$ STI $,$ ClrInt $

- 节拍$ T_3 $:$ EPC\rightarrow PC $,$ 1\rightarrow IE $,恢复断点并开中断

- 为了支持中断添加的相关支持